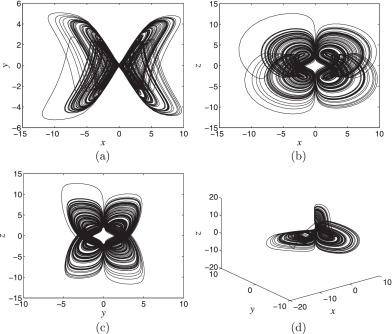

Four-wing attractors in a novel chaotic system with hyperbolic sine nonlinearity

Chaotic systems generating multi-wing attractors have received considerable attention in the literature. In this work, we propose a novel three-dimensional chaotic system with hyperbolic sine nonlinearity. It is worth noting that the system is elegant and includes only one parameter. Despite its simple structure, the new system displays double-wing and four-wing chaotic attractors. By studying dynamics of the system, coexistence of limit cycles or chaotic attractors is discovered. The capable of the synchronization of new chaotic system is verified by using an adaptive control. Furthermore, an

Controllable OTA Slew-rate for CMOS Image Sensor

In this work, a proposed circuit is implemented using tsmc 0.18um technology of area 16642 um2 with supply voltage equals 5V. A proposed implementation of a controllable Operational Transconductance Amplifier (OTA) slew rate for CMOS image sensor (CIS) is proposed. The slew rate is controlled by switching between various bias circuits for the OTA. The biasing circuit controls the value of OTA biased current, which allows controlling the amplifier's characteristics. As the flicker noise in the main contributor in reducing the quality of image sensors performance. The proposed circuit allows

Cad tool for two-digit ternary functions design

Ternary number, which attracts the research attention for its high capacity, has emerged in many applications, recently. Unlike binary numbers, two bit ternary number involves 93 = 729 different functions while two bit binary number involves only 42 = 16 different possible functions. In this paper, a novel automatic software description two bits ternary functions design tool is presented. Different examples are provided and synthesized to ternary logic circuits. Finally, the presented logic circuits are verified by SPICE simulation using carbon nano-Tube (CNTFET) transistors. © 2019 IEEE.

Fibonacci-based hardware post-processing for non-autonomous signum hyperchaotic system

This paper presents a hardware implementation of a robust non-autonomous hyperchaotic-based PRNG driven by a 256-bit LFSR. The original chaotic output is post-processed using a novel technique based on the Fibonacci series, bitwise XOR, rotation, and feedback. The proposed post-processing technique preserves the throughput of the system and enhances the randomness in the output which is verified by successfully passing all NIST SP. 800-22 tests. The system is realized on a Xilinx Virtex 4 FPGA achieving throughput up to 13.165 Gbits/s for 16-bit bus-width surpassing previously reported CB

FPGA implementation of a configurable viterbi decoder for software radio receiver

Convolutional codes are one of the Forward Error Correction (FEC) codes that are used in every robust digital communication system. Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. Software Defined Radio (SDR) is realized using highly configurable hardware platforms. Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in SDR. In this paper, a generic, configurable and low power Viterbi decoder for

FPGA implementation of a reconfigurable Viterbi decoder for WiMAX receiver

Field Programmable Gate Array technology (FPGA) is a highly configurable option for implementing many sophisticated signal processing tasks in Software Defined Radios (SDRs). Those types of radios are realized using highly configurable hardware platforms. Convolutional codes are used in every robust digital communication system and Viterbi algorithm is employed in wireless communications to decode the convolutional codes. Such decoders are complex and dissipate large amount of power. In this paper, a low power-reconfigurable Viterbi decoder for WiMAX receiver is described using a VHDL code for

Advance Interconnect Circuit Modeling Design Using Fractional-Order Elements

Nowadays, the interconnect circuits' conduct plays a crucial role in determining the performance of the CMOS systems, especially those related to nano-scale technology. Modeling the effect of such an influential component has been widely studied from many perspectives. In this article, we propose a new general formula for RLC interconnect circuit model in CMOS technology using the fractional-order elements approach. The study is based on approximating an infinite transfer function of the CMOS circuit with a noninteger distributed RLC load to a finite number of poles. It is accurate due to the

Towards Mobility-Aware Proactive Caching for Vehicular Ad hoc Networks

Harnessing information about the user mobility pattern and daily demand can enhance the network capability to improve the quality of experience (QoE) at Vehicular Ad- Hoc Networks (VANETs). Proactive caching, as one of the key features offered by 5G networks, has lately received much interest. However, more research is still needed to convey large-sized multimedia content including video, audio and pictures to the high speed moving vehicles. In this paper, we study the gains achieved by proactive caching in Roadside Units (RSUs) where we take into consideration the effect of the vehicle

Towards optimal resource allocation in caching at relay networks

We investigate the performance of caching in relay networks where an intermediate relay station (RS) caches content for future demand by end users. With uncertain user demand over multiple data items and dynamically changing wireless links, we characterize the optimal transmission time for serving data items, cached data portion allocation of relay station and optimal service portion, which represents a part from the cached portion, to minimize the total average transmission energy. We argue that under several settings fully caching the higher popular items is the optimal caching policy which

Towards optimal power control for delay-constrained cognitive radio networks

In this paper we study the problem of optimal power control for a Z-interference channel abstracting an underlay cognitive radio network where the secondary user has delay constraints. More specifically, we minimize the packet drop probability at the secondary user (equivalent to delay bound violation probability) subject to quality of service (QoS) constraints at the primary and secondary users, among other constraints. Towards, this objective, we develop a mathematical framework using Markov chains and formulate a constrained optimization problem. First, we assess the complexity of the

Pagination

- Previous page ‹‹

- Page 13

- Next page ››