Generalized fractional logistic map encryption system based on FPGA

This paper introduces the design of a generalized fractional order logistic map suitable for pseudorandom number key generators and its application in an encryption system based on FPGA. The map is generalized through two parameters (a,b) where complete analysis of their effect on the map is detailed, which gives more control on the map chaotic regions. The vertical map and the zooming map presented in this paper are two special maps extracted from the generalized map with their detailed analysis. Not only the positive bifurcation, but also the negative side is discussed through this paper

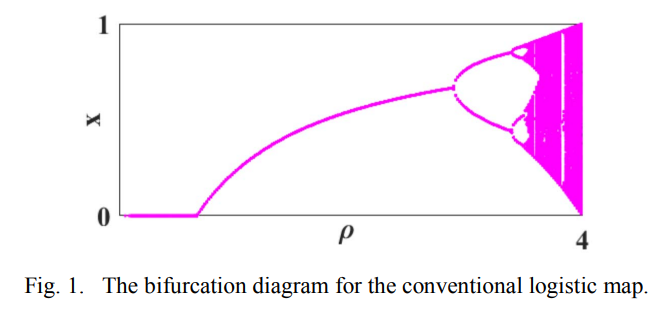

Dynamics of fractional and double-humped logistic maps versus the conventional one

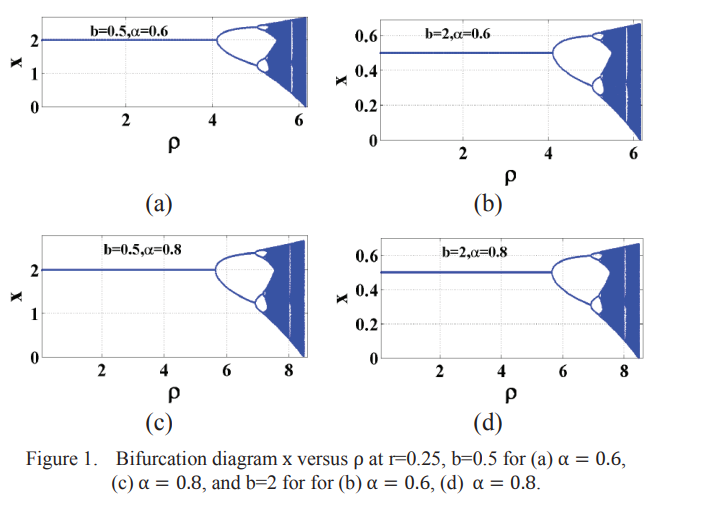

This paper presents the dynamic analysis of two discrete logistic chaotic maps versus the conventional map. The first map is the fractional logistic map with the extra degrees of freedom provided by the added number of variables. It has two more variables over the conventional one. The second map is the double-humped logistic map. It is a fourth-order map which increases the non-linearity over the conventional one. The dynamics of the three maps are discussed in details, including mathematical derivations of fixed points, stability analysis, bifurcation diagrams and the study of their chaotic

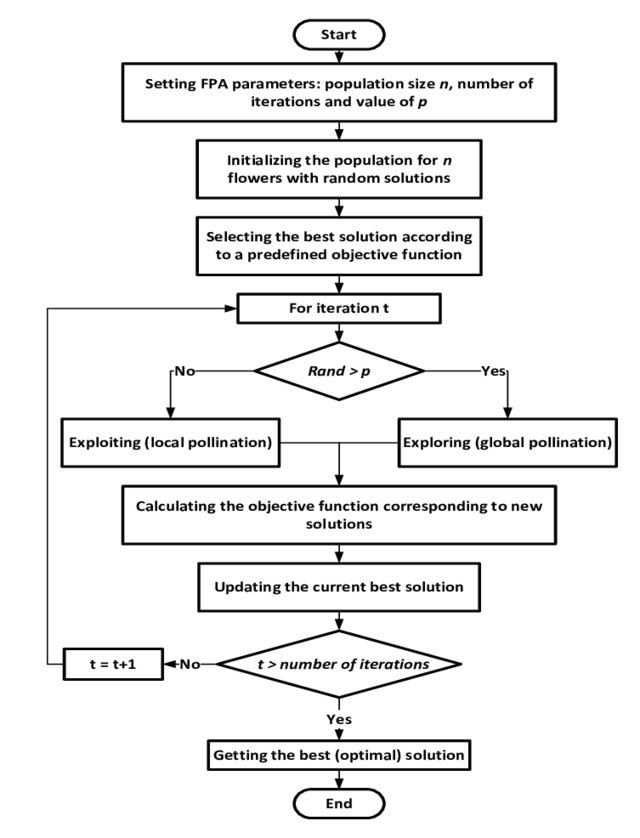

A Novel Power-Aware Task Scheduling for Energy Harvesting-Based Wearable Biomedical Devices Using FPA

Power management and saving in energy harvesting-based biomedical wearable devices are mandatory to ensure prolonged and stable operation under a stringent power budget. Thus, power-aware task scheduling can play a key role in minimizing energy consumption to improve system durability while maintaining device functionality. This paper proposes a novel biosensor task scheduling for optimizing energy consumption through wearable biomedical devices. The proposed approach is based on Flower Pollination Algorithm (FPA). The biomedical functionality constraints are enforced with a Hamming-based

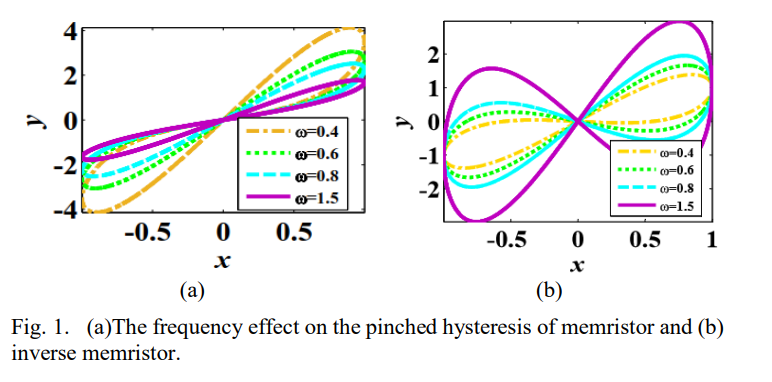

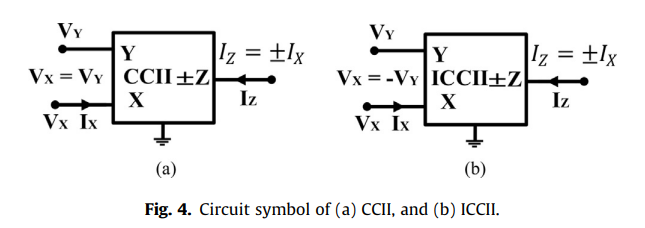

Inverse memrsitor emulator active Realizations

The paper aims to propose three different inverse memristor emulators based on serveral active blocks. One of the presented emulator realizes employing second generation current conveyor (CCII) andcanalog voltage multiplier with passive elements. The other two introduced emulators are designed using cureent feedback operational amplifier (CFOA) with two switches or two BJT transistor. One of the proposed emulators has the advantages that it switches between the inverse and memristor at the same time but in different frequency with less number of components. The introduced circuitry are

Generalized delayed logistic map suitable for pseudo-random number generation

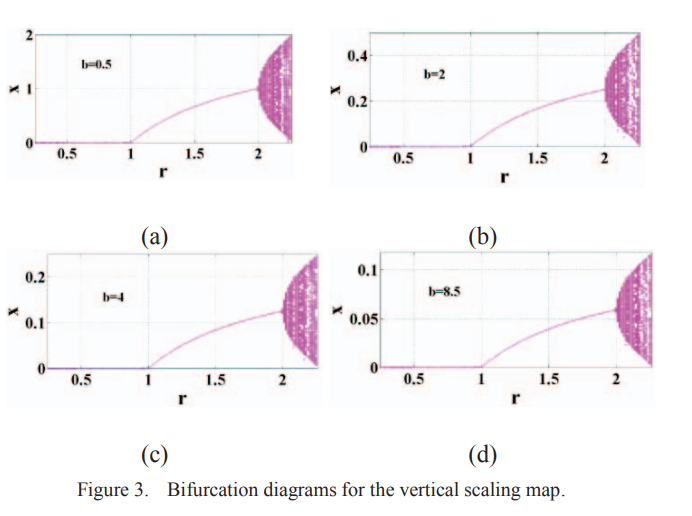

This paper presents the generalization of a delayed version of the logistic map. The effect of the added two general parameters is studied, which offers the option of having three different maps. The dynamic behavior of the vertical, zooming and the general map is analyzed. The study of the fixed points, stability ranges and bifurcation diagram of the delayed logistic map at hand is detailed in this work. The flow of the system behavior from stability to chaos is also presented with its transient response as well as its phase plane portraits. Moreover, using the general parameters, the option

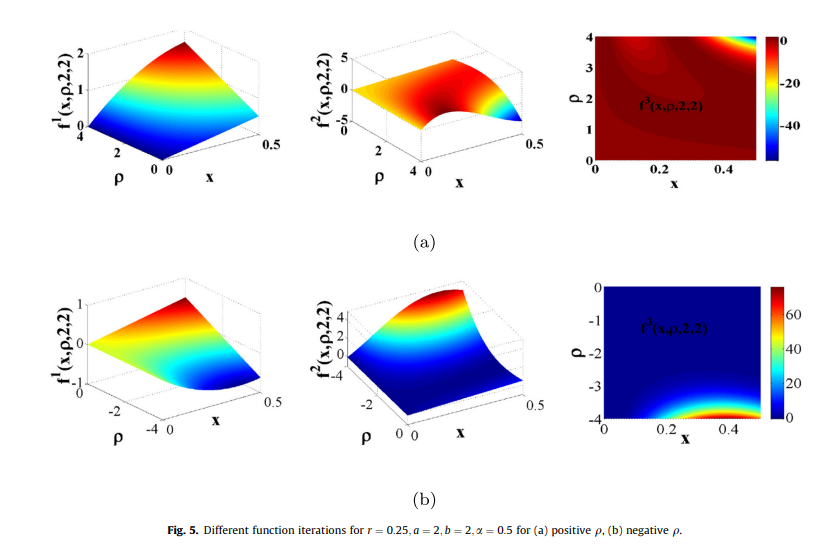

Generalized fractional logistic map suitable for data encryption

This paper presents a generalized form of the fractional logistic map. Two general parameters a and b are added to the classical fractional logistic equation. The effect of such parameters on the map is studied explicitly, in combination with the fractional order parameter α, which offers an extra degree of freedom increasing the design flexibility and adding more controllability on the design. The vertical and the zooming map are two special maps that arise as a result of the added parameters. Moreover, different design problems are offered in this work, as a resultant of the control of all

On The Optimization of Fractional Order Low-Pass Filters

This paper presents three different optimization cases for normalized fractional order low-pass filters (LPFs) with numerical, circuit and experimental results. A multi-objective optimization technique is used for controlling some filter specifications, which are the transition bandwidth, the stop band frequency gain and the maximum allowable peak in the filter pass band. The extra degree of freedom provided by the fractional order parameter allows the full manipulation of the filter specifications to obtain the desired response required by any application. The proposed mathematical model is

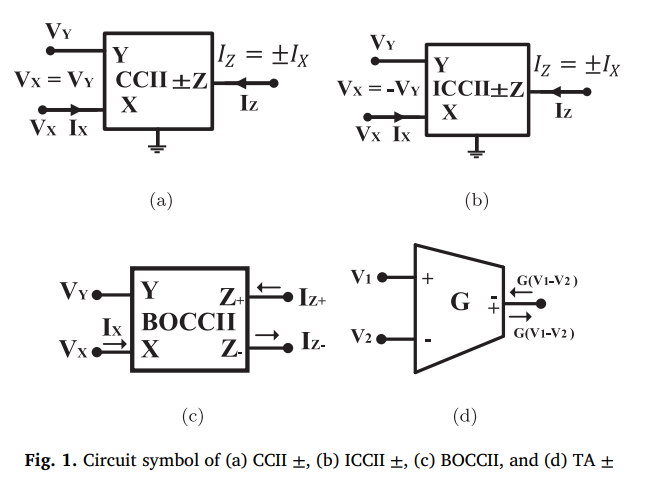

On the analysis of current-controlled fractional-order memristor emulator

In this paper, a current-controlled fractional-order memristor model and its emulator are proposed. The emulator is built using two second generation current conveyor (CCII) and fractional-order capacitor. It is shown that the effect of the fractional order is clearly noticeable in the circuit response. PSPICE simulations are introduced for different values of the fractional order showing noticeable variations of the pinched-loop hysteresis curves. The fractional order model shows wider frequency of operation and larger pinched loop hysteresis area than the integer one. © 2017 IEEE.

Generalized two-port network based fractional order filters

This paper proposes a general prototype fractional order filter based on a two-port network concept with four external impedances. Three induced classifications from the general prototype are extracted with one, two and three external impedances, achieving ten possible generalized topologies. The external impedances are fractional-order elements and resistors. There are forty-six filters divided into twenty-two and twenty-four different general fractional filters of order “α” and order “α + β”, respectively. The general transfer functions, the necessary network conditions, and the critical

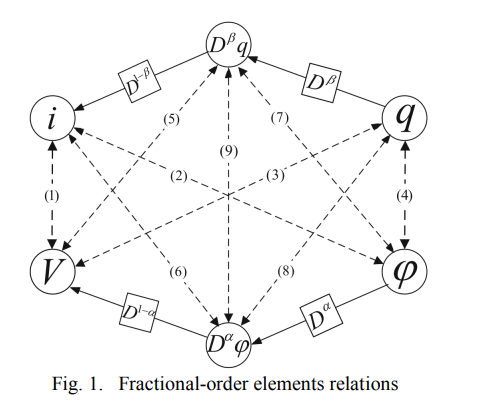

General fractional order mem-elements mutators

This paper proposes the realization of grounded and floating fractional order mem-elements (FOMEs) based on two- and three-port mutators, respectively. Three different topologies based on two-port mutators are implemented using the four members of the second-generation current conveyor (CCII) family which is useful to achieve several realizations for the same circuit. The Fractional Order Mem-capacitor (FOMC) and Fractional Order Mem-inductor (FOMI) are realized using different combinations of memristor and fractional order capacitor (FOC) plus resistors. In addition, the generalization of the

Pagination

- Previous page ‹‹

- Page 17

- Next page ››