Generalized hardware post-processing technique for chaos-based pseudorandom number generators

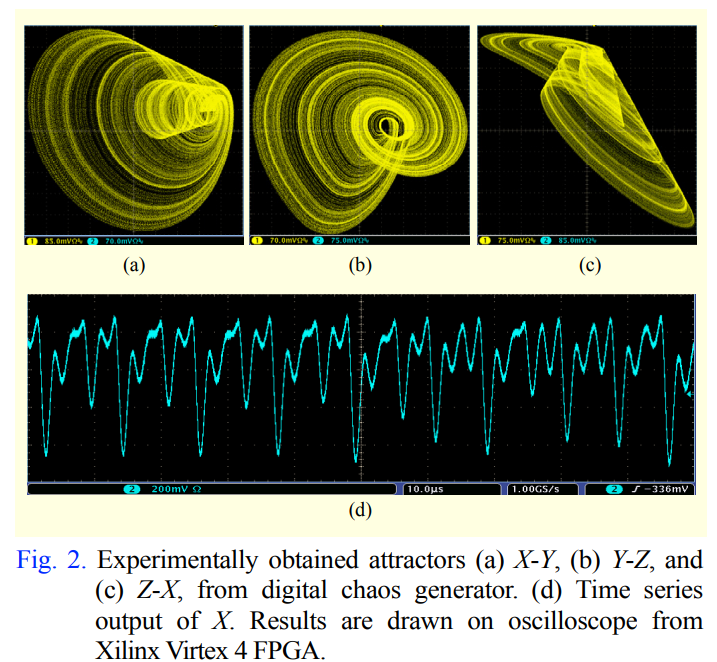

This paper presents a generalized post-processing technique for enhancing the pseudorandomness of digital chaotic oscillators through a nonlinear XOR-based operation with rotation and feedback. The technique allows full utilization of the chaotic output as pseudorandom number generators and improves throughput without a significant area penalty. Digital design of a third-order chaotic system with maximum function nonlinearity is presented with verified chaotic dynamics. The proposed post-processing technique eliminates statistical degradation in all output bits, thus maximizing throughput

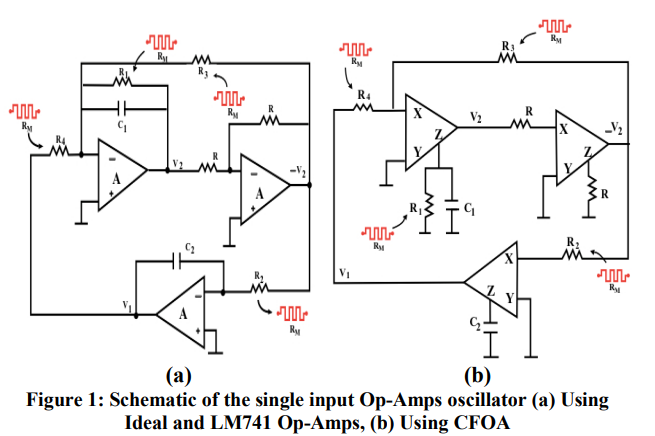

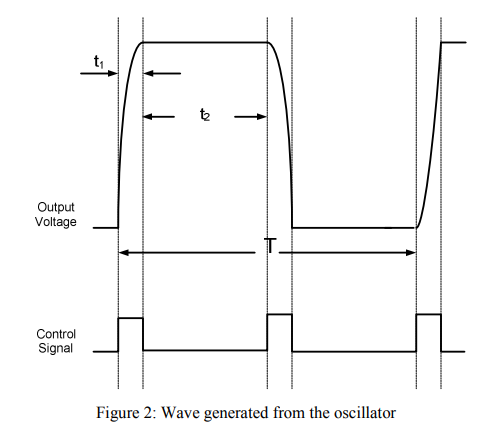

The modified single input Op-Amps memristor based oscillator

This paper introduces the modified single input Op-Amps memristor based oscillator. The oscillator is realized with ideal, LM741 and current feedback (AD844) Op-Amps where memristors replace resistors. The effect of memristor on the oscillation frequency and the oscillation condition that are totally independent is studied. This helped in studying the whole operation regime of the memristor. The effect of initial conditions on the circuit behavior is discussed. The dynamic poles of the oscillator after resistors replacement are illustrated. Sustained oscillation is obtained and simulated

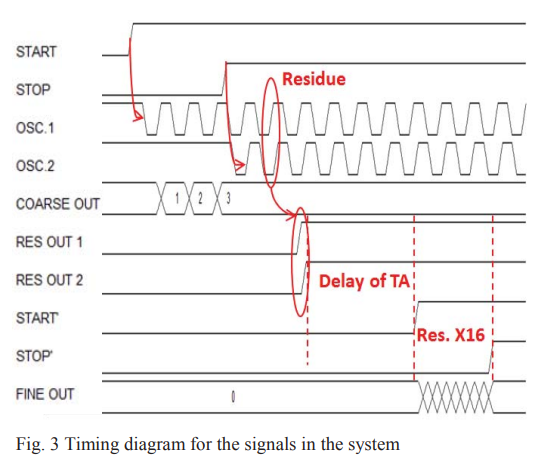

A novel high throughput high resolution two-stage oscillator-based TDC

This paper presents a new technique to reduce the conversion time, hence improve the throughput, of the two-stage Time to Digital Converter (TDC) architecture. An oscillator based TDC is used in the first and second stages. The time residue from the first stage is generated directly after the stop signal is asserted and saved in the form of phase-shift between two oscillating signals. A throughput of 400 MS/s, a DNL of 0.38, and an INL of 0.36 are achieved. © 2013 IEEE.

Current source based standard-cell model for accurate timing analysis of combinational logic cells

Timing verification is an essential process in nanometer design. Therefore, static timing analysis (STA) is currently the main aspect of performance verification. Traditional STA is based on lookup tables with input slew and output load capacitance. It is becoming insufficient to accurately characterize many significant aspects of the conventional cell delays models, such as: the process variations, nonlinear waveforms, nonlinear loads, and multiple inputs switching (MIS). Therefore, the current trend in modern designs is to use current source based models (CSM), which model MOSFETs as a

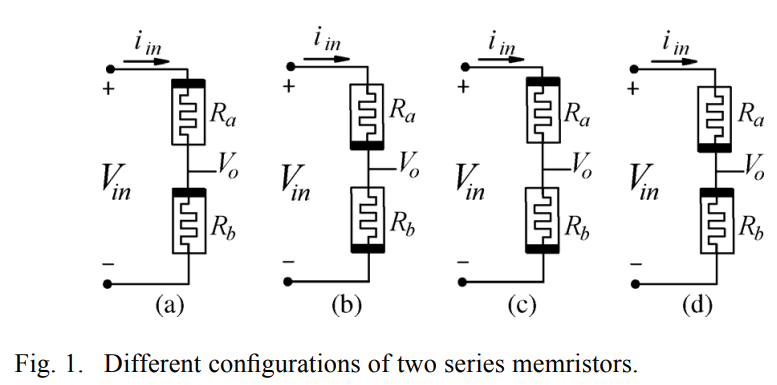

Generalized analysis of symmetric and asymmetric memristive two-gate relaxation oscillators

Memristive oscillators are a novel topic in nonlinear circuit theory, where the behavior of the reactive elements is emulated by the memristor. This paper presents symmetric and asymmetric memristive two-gate relaxation oscillators. First, the analysis of the two series memristors is introduced to study the effect of changing their polarities, as well as the mobility factor to be used in the two-gate relaxation oscillator instead of the RC circuit. The generalized analysis for the proposed memristive two-gate oscillator is introduced, where the generalized expressions for the oscillation

Design methodology for square wave resonant clock generators

Resonant clocking is a promising low power alternative for conventional clocking method. In this work, a design methodology is presented for square wave resonant clocking technique to assure minimum power consumption. These equations were verified by designing a differential clock generator which showed 55% power savings compared to conventional clocking. © 2012 IEEE.

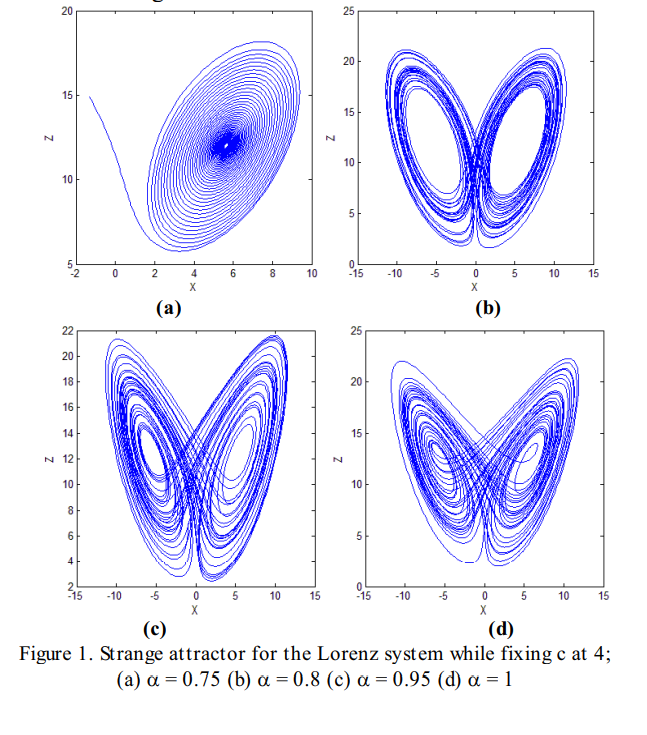

Image encryption in the fractional-order domain

This paper presents a new image encryption scheme based on the fractional-order Lorenz system which gives more degrees of freedom in key generation. In the modified fractional-order system, the key length is doubled using the three fractional-orde r parameters beside the three initial conditions, which makes it invulnerable to brute-force attacks. In addition, using a very simple algorithm, based on pixel confusion only, strongly encrypted images are produced. Such an algorithm can be used in real time applications. To evaluate the algorithm and analyze the encryption results, a standard image

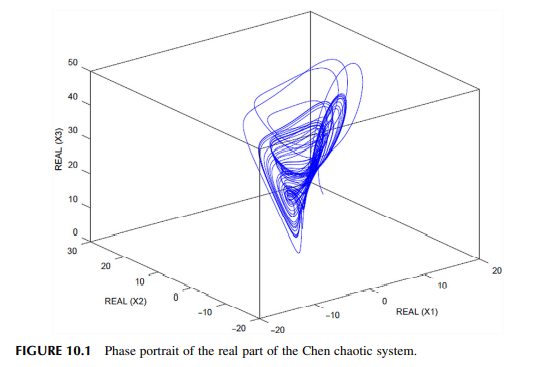

Sliding mode stabilization and synchronization of fractional order complex chaotic and hyperchaotic systems

This chapter is intended to design and analyze several sliding mode techniques for the stabilization and synchronization of fractional order complex chaotic and hyperchaotic systems. Considering that chaos is a hot topic nowadays due to the vast number of real physical systems such as mechanical, electrical, and chemical systems in which this phenomenon is found; this book chapter will provide novel sliding mode approaches for the stabilization and synchronization of chaotic and hyperchaotic systems. Fractional order chaotic and hyperchaotic systems have been proved to be difficult to

A 4-D chaotic hyperjerk system with a hidden attractor, adaptive backstepping control and circuit design

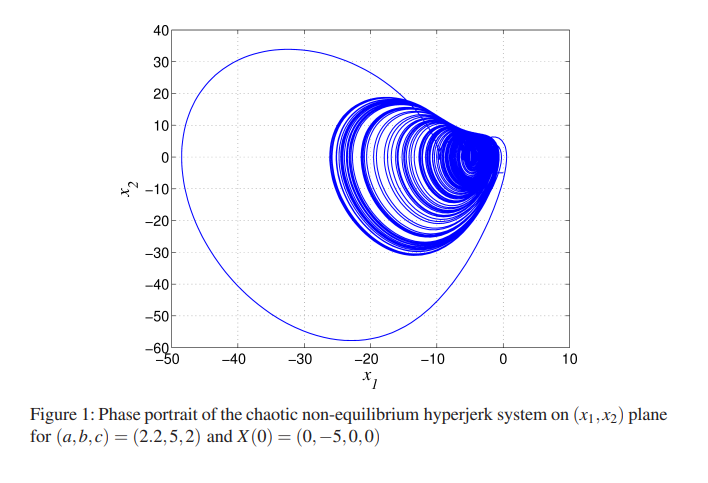

A novel 4-D chaotic hyperjerk system with four quadratic nonlinearities is presented in this work. It is interesting that the hyperjerk system has no equilibrium. A chaotic attractor is said to be a hidden attractor when its basin of attraction has no intersection with small neighborhoods of equilibrium points of the system. Thus, our new non-equilibrium hyperjerk system possesses a hidden attractor. Chaos in the system has been observed in phase portraits and verified by positive Lyapunov exponents. Adaptive backstepping controller is designed for the global chaos control of the non

Pagination

- Previous page ‹‹

- Page 53

- Next page ››