On the mechanism of creating pinched hysteresis loops using a commercial memristor device

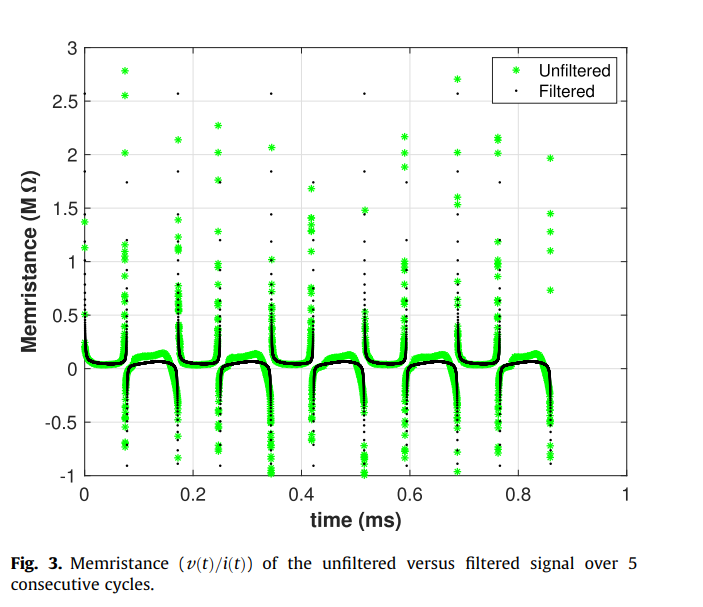

In this short communication we analyze the impact of signal harmonics on the formation of the pinched hysteresis loop using a commercial memristor device. We show that by using only the fundamental frequency and the second harmonic components, extracted from the measured electrical current signal, a distortion-less pinched hysteresis loop is re-created. This loop is then used to simulate memristor-based AND/OR gates without any loss in digital functionality. This verifies that the generation of a pinched hysteresis loop requires a nonlinear frequency doubling mechanism to create a second

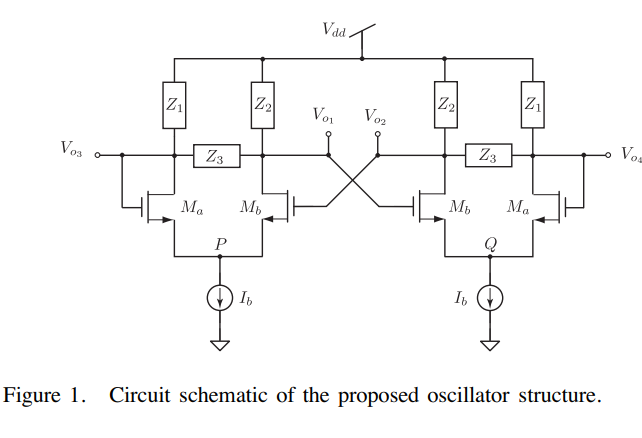

Third-order tunable-phase asymmetric crosscoupled oscillator

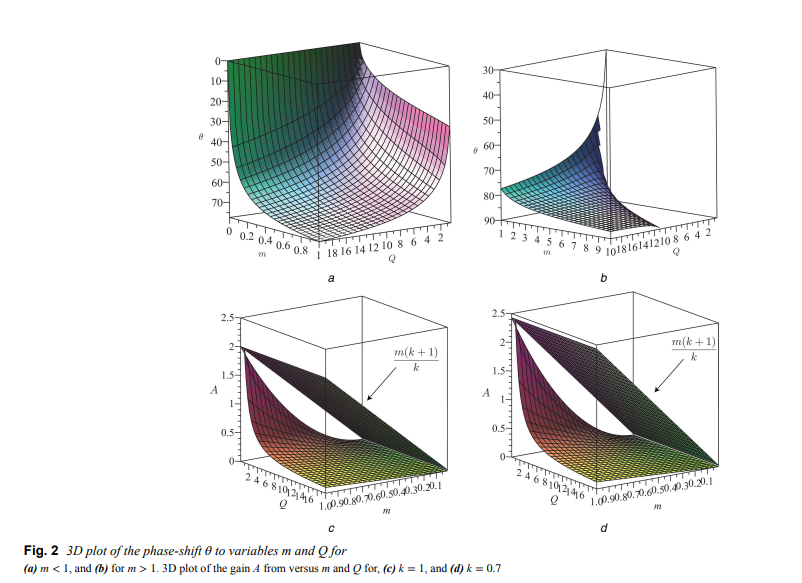

Here, the authors show that an asymmetric cross-coupled oscillator can be used to achieve independent-phase tunable outputs. In particular, a third-order cross-coupled oscillator, with non-balanced loads, is studied and expressions for its start-up condition, oscillation frequency, phase-shift between its two outputs as well as their amplitude ratio are derived. From these expressions, it is found that independent tuning of these design specifications is possible and a voltage-controlled phasetunable oscillator can be achieved. As a consequence of the non-balanced loads, the tail biasing

Single-Transistor Second-Order Allpass Filters

This paper presents two CMOS designs of a second-order voltage-mode allpass filters (APFs) for high-frequency applications. Each of the proposed filters is based only on a single transistor and four surrounding impedances. The first proposed allpass filter is an RL filter while the second proposed one is an RLC filter. A detailed analysis along with the parasitic effects is provided for each of the proposed filters. As a proof of concept, one design was constructed and verified experimentally using discrete MOS transistors at a 2.3MHz pole frequency. The experimental results showed a group

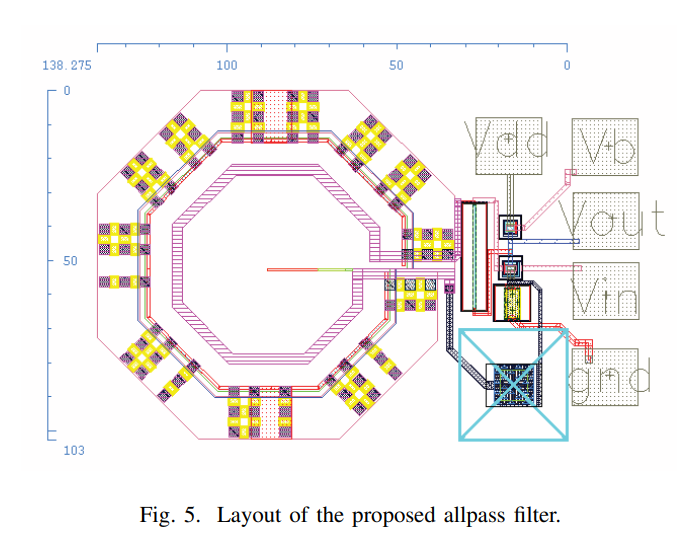

An Ultra-Low Power Wide-Band Single-Transistor Second-Order Allpass Filter in 65nm CMOS

In this paper, we propose a MOS design of a second-order voltage-mode allpass filter to be used as a time delay cell. The proposed filter is based on a single transistor, three resistors and two energy storage elements and was designed in a 65nm CMOS technology. Post-layout simulations demonstrate a group delay of approximately 13ps across a 30GHz bandwidth, while only consuming 809.7μW from a 1-V supply. As a proof of concept, the proposed filter was constructed and verified experimentally using discrete MOS transistors. The experimental results show a group delay of approximately 370ns

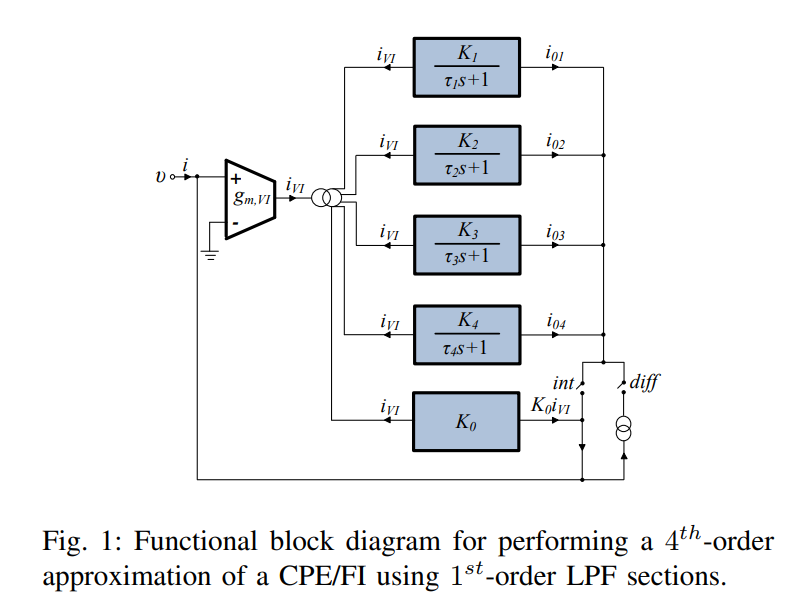

Log-domain implementation of fractional-order element emulators

Novel fractional-order capacitor and inductor em-ulators are presented in this work, which offer fully electronic tunability of their characteristics and, simultaneously, reduced circuit complexity compared to those already introduced in the literature. This has been achieved through the utilization of the log-domain filtering for implementing the approximation of the required fractional-order differentiation/integration stages. The behavior of the presented topology is evaluated using the Cadence software and MOS transistor models provided by the 0.35μm Austria Mikro Systeme CMOS process. ©

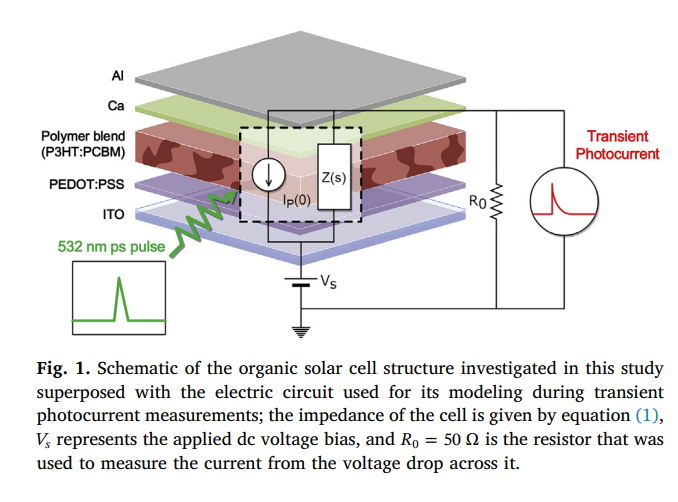

On the modeling of dispersive transient photocurrent response of organic solar cells

The current methods used for estimating the electrical parameters of organic solar cells (OSC) from time-domain measurements are based on integer-order impedance models. Meanwhile, in the frequency-domain, the adopted circuit models usually contain a constant phase element which is known to capture effectively the fractional-order dispersive behavior of these devices. Therefore, inconsistency arises between the two analyses. In this work, we derive the time-domain relaxation response of an OSC, found to follow a Mittag-Leffler function, using the same fractional-order impedance model. The

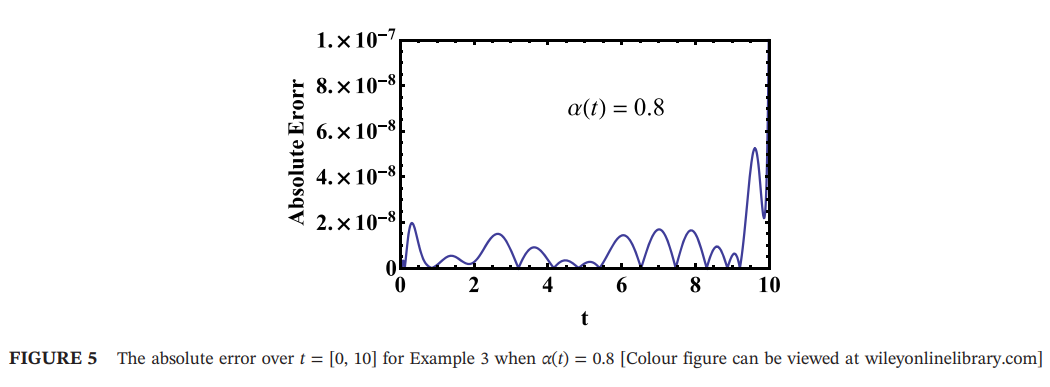

The minimax approach for a class of variable order fractional differential equation

This paper introduces an approximate solution for Liouville-Caputo variable order fractional differential equations with order 0

On a class of quadrature phase oscillators using differential pairs

A new class of quadrature phase oscillators based on cross-coupled differential pairs is introduced. This class contains eight possible circuits which produce four output voltages with phase differences of ±π or ±π/2, depending on the choice of output node, and does not require balanced differential-pair loads. Phase error analysis is provided along with experimental and simulation results using discrete MOS and BJT transistors as a proof of concept. © 2018 IEEE

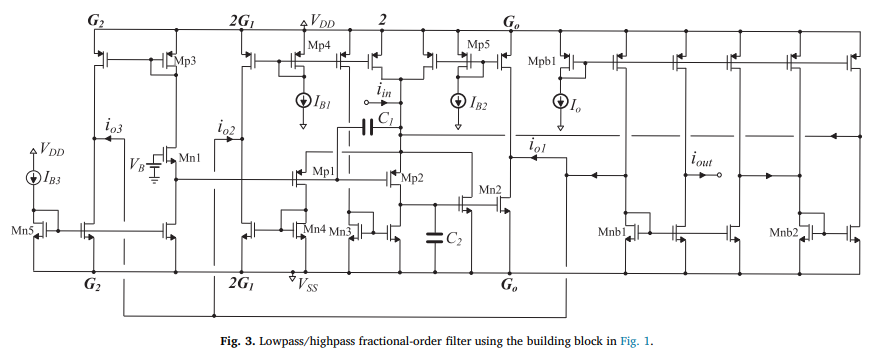

Design and application examples of CMOS fractional-order differentiators and integrators

Reduced complexity CMOS fractional-order differentiator and integrator building blocks are introduced in this work, based on 2 nd -order integer-order transfer function approximations. These blocks are then used for implementing fractional-order filters as well as a Leaky-Integrate-and-Fire Mihalas-Niebur neuron model. Cascading 1 st and 2 nd -order blocks to obtain 5 th -order integer-order transfer functions, improved bandwidth of approximation accuracy is achieved. Furthermore, the realization of fractional-order capacitor and inductor emulators is demonstrated. © 2018 Elsevier Ltd

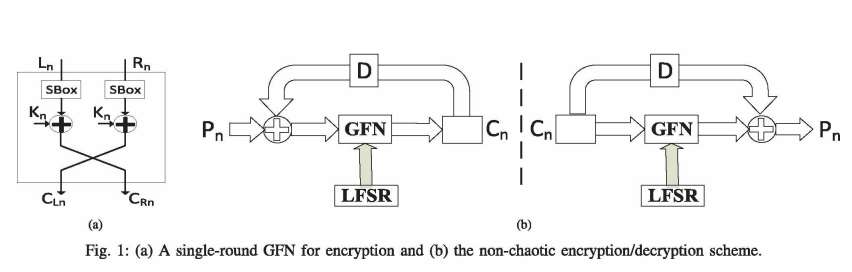

Security and Efficiency of Feistel Networks Versus Discrete Chaos for Lightweight Speech Encryption

This paper compares examples of non-chaotic and chaotic ciphers from the viewpoint of their suitability for speech encryption, especially in real-time and lightweight cipher systems. The non-chaotic encryption scheme depends on a modified Generalized Feistel Network (GFN), Linear Feedback Shift Register (LFSR) and Substitution Boxes (S-Boxes). The chaotic encryption scheme utilizes a generalized modified tent map with multiple modes of operation. The security and efficiency of both schemes are analyzed using the perceptual tests: time waveform and spectrogram; the statistical tests: histogram

Pagination

- Previous page ‹‹

- Page 49

- Next page ››