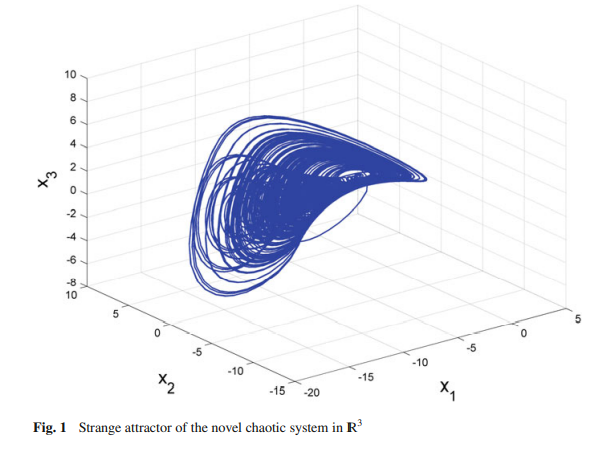

An eight-term 3-D novel chaotic system with three quadratic nonlinearities, its adaptive feedback control and synchronization

This research work describes an eight-term 3-D novel polynomial chaotic system consisting of three quadratic nonlinearities. First, this work presents the 3-D dynamics of the novel chaotic system and depicts the phase portraits of the system. Next, the qualitative properties of the novel chaotic system are discussed in detail. The novel chaotic system has four equilibrium points. We show that two equilibrium points are saddle points and the other equilibrium points are saddle-foci. The Lyapunov exponents of the novel chaotic system are obtained as L1 = 0.4715, L2 = 0 and L3 = -2.4728. The

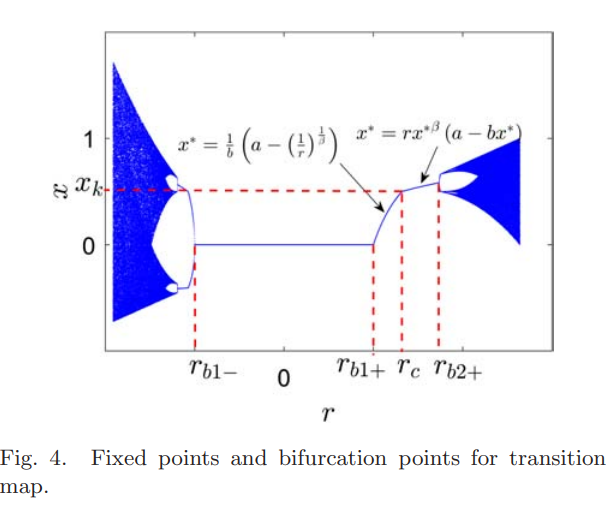

Generalized smooth transition map between tent and logistic maps

There is a continuous demand on novel chaotic generators to be employed in various modeling and pseudo-random number generation applications. This paper proposes a new chaotic map which is a general form for one-dimensional discrete-time maps employing the power function with the tent and logistic maps as special cases. The proposed map uses extra parameters to provide responses that fit multiple applications for which conventional maps were not enough. The proposed generalization covers also maps whose iterative relations are not based on polynomials, i.e. with fractional powers. We introduce

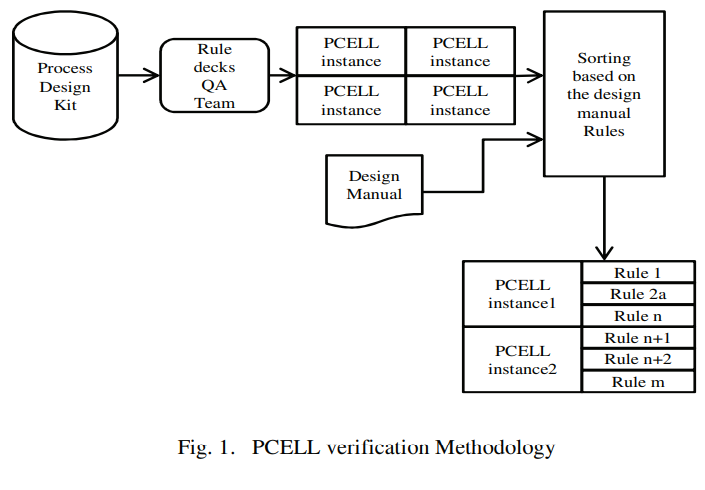

Parameterized test patterns methodology for layout design rule checking verification

Design rules verification is an essential stage in the Process Design Kit (PDK) release for any fab. Since achieving high yield is the target of any fab, the design rules should ensure this. Design rules violations happening after fabrication lead to disastrous results on the mask sets as well as increased cost and delayed schedules. Here comes the importance of verifying these design rules and making sure that they represent the process in a manner that achieves a high yield and detects design rules issues early on. The verification process consumes 60% of the release cycle and the most time

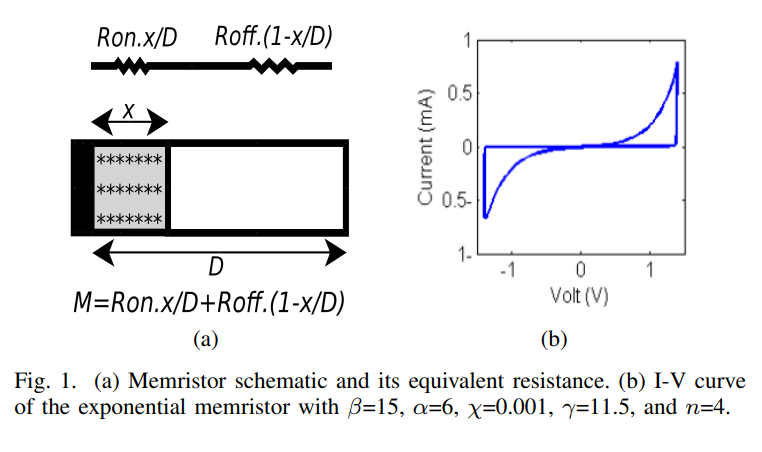

2T2M memristor-based memory cell for higher stability RRAM modules

This paper introduces a novel 2T2M memristor based memory cell which, offers higher stability and noise margins than previous works. The proposed 2T2M RRAM module is similar to conventional 6T SRAM module in terms of delay and number of interface pins. However, the predicted area of the proposed 2T2M RRAM cell is significantly lower compared to the CMOS based 6T SRAM cell, and is also expected to consume lower energy. The nonvolatile characteristics of the cell make it more attractive for nonvolatile random access memory design. Write, read and repeated read operations of the proposed 2T2M

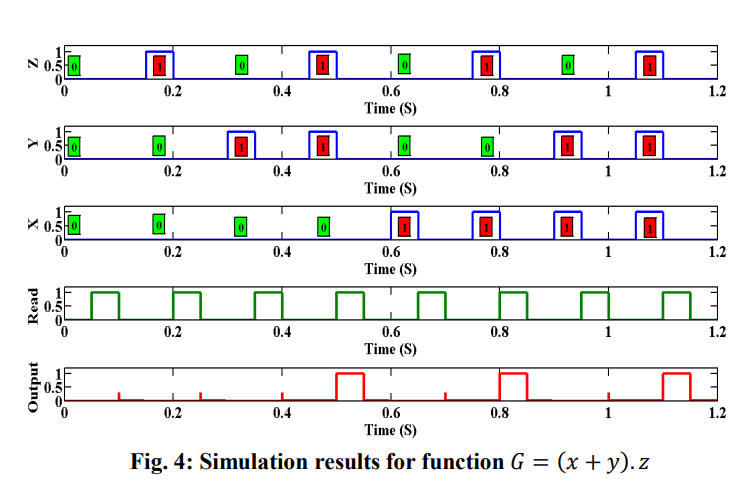

Memristor-MOS hybrid circuit redundant multiplier

This paper introduces a step forward towards memristor-MOS hybrid circuit to achieve any combinational function. The proposed design is based on reducing the area by replacing the complete pull-down network with just one memristor and one comparator. The concept is then verified using an example of a simple function. Also, a proposed architecture for memristor based redundant multiplier circuit is introduced and verified using the SPICE simulation. Therefore, any redundant functions can be implemented using the same concept. © 2014 IEEE.

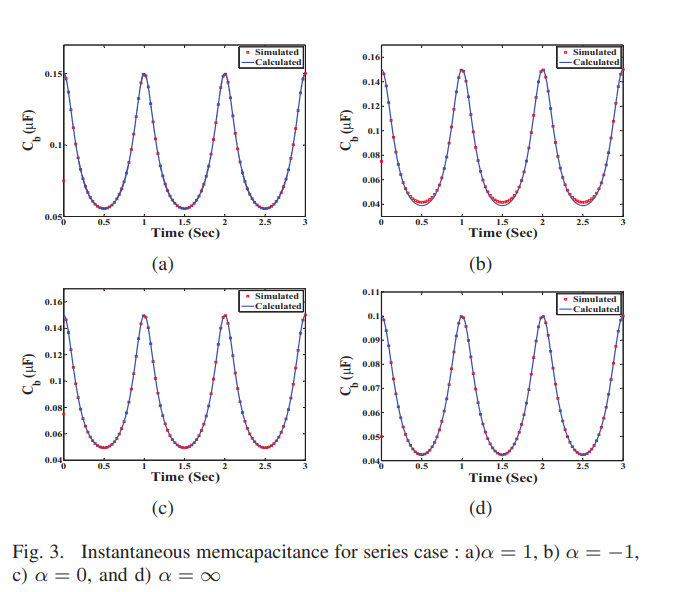

On the mathematical modeling of series and parallel memcapacitors

Recently, Memristive elements such as memristor, memcapacitor and meminductors have become very attractive components in many applications, due to its unique behavior which can not be obtained using the other conventional elements. This paper discusses the analytical analysis of two memcapacitors connected in series and in parallel taking the effect of mismatch in mobility factor and polarity of each one. The obtained formulas of instantaneous memcapacitance for each memcapacitor are derived and four special cases are analyzed in more details. The proposed special cases are validated using

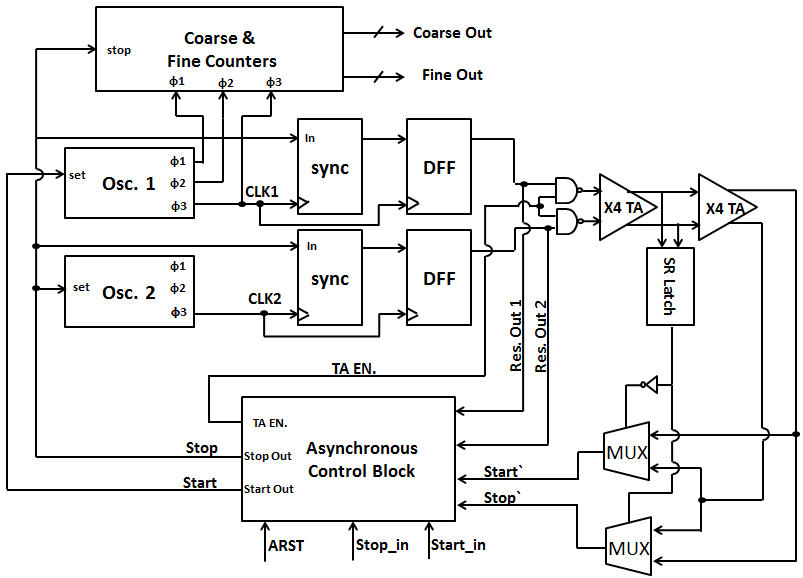

A novel 10-Bit high-throughput two-stage TDC with reduced power and improved linearity

This paper introduces a new architecture that improves the throughput of the two-stage Time to Digital Converter (TDC). An oscillator-based TDC is used for conversion. The time residue from the first stage is generated directly after the stop signal is asserted and saved in the form of phase-shift between two oscillating signals. Instead of using two stages, an asynchronous control block is implemented to reuse the same hardware block for both the first and second conversion stages. This technique not only reduces power and area, but also eliminates the TDC nonlinearity due to the mismatch

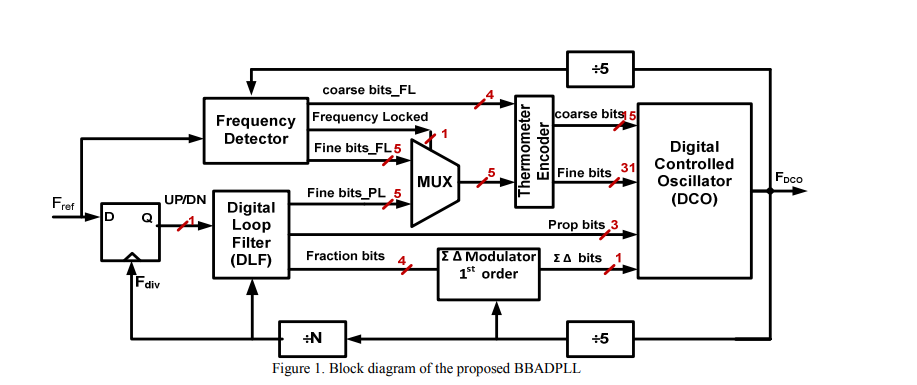

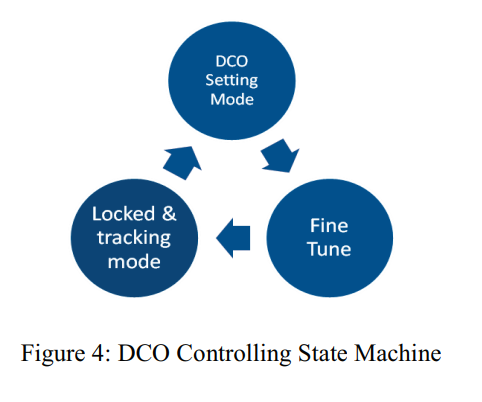

A 5-10GHz low power bang-bang all digital PLL based on programmable digital loop filter

This paper presents the design and the implementation of a low power bang-bang all digital phase locked loop (BBADPLL). The design of the proposed architecture is based on the programmable coefficients of the digital loop filter (DLF) that manages the tradeoffs between stability and jitter of a closed loop. A proposed simple digital controlled oscillator (DCO) based on three stages ring oscillator provides a wide frequency range, and proven to be of lower area and power compared to arrayed DCO. The proposed design results in a significant reduction in the area and power compared to other time

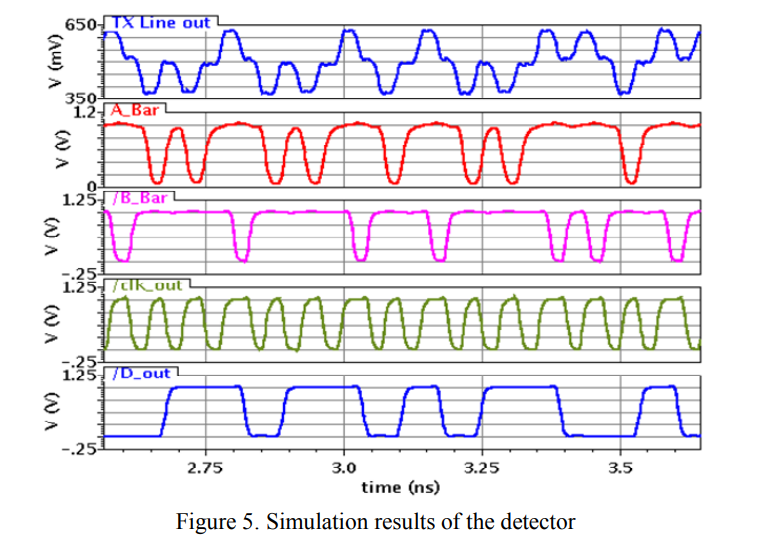

A 16Gbps low power self-timed SerDes transceiver for multi-core communication

This paper presents a modified design for a self-timed SerDes transceiver that was recently published [1]. The new architecture overcomes the main problems that arise in [1], while offering the same advantages. Resistive termination is used instead of source matching to eliminate the need for Manchester coding in [1], this resistive termination increased the data rate to be 16Gbps compared to 12Gbps in [1]. Moreover, resistive termination removed the limitation on the minimum operating frequency that existed in [1], solving a lot of problems at the slow process corners. A single ended

A novel power gated digitally controlled oscillator

In this paper a novel power gated digitally controlled oscillator (DCO) is presented. The DCO is suitable for integration in various systems such as clock generation circuits, clock and data recovery, and clocking schemes for high speed links. Simulations of the proposed DCO on 65nm TSMC technology show frequency range of 2.5 GHz to 6.8 GHz across all corners. The proposed DCO consumes only 1.7 mW at 3 GHz and 3.2 mW at 6.8 GHz with estimated layout area of 70 *70 m 2. The phase noise of the free running DCO is 92 dBc/Hz measured at 1 MHz offset from a 3.4 GHz center frequency. © 2011 IEEE.

Pagination

- Previous page ‹‹

- Page 40

- Next page ››